目录

PCIE物理层-encoder

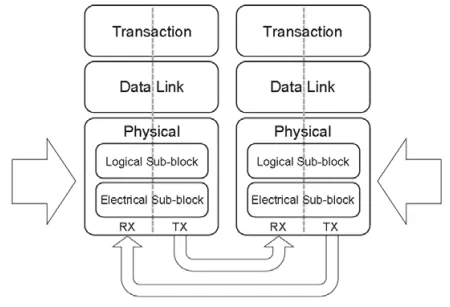

PCIE的物理层框图如下

对于PCIE的传输编码,如果在pcie1.0和pcie2.0,则使用8/10b的编码,如果是pcie3.0及以上,则使用128/130b传输编码

对于pcie3.0,默认是8GT/s,如果传输编码大于等于8GT/s,则默认使用128/130b编码,如果pcie3.0在L0状态,则默认是2.5GT/s传输,则此时使用8/10b编码。

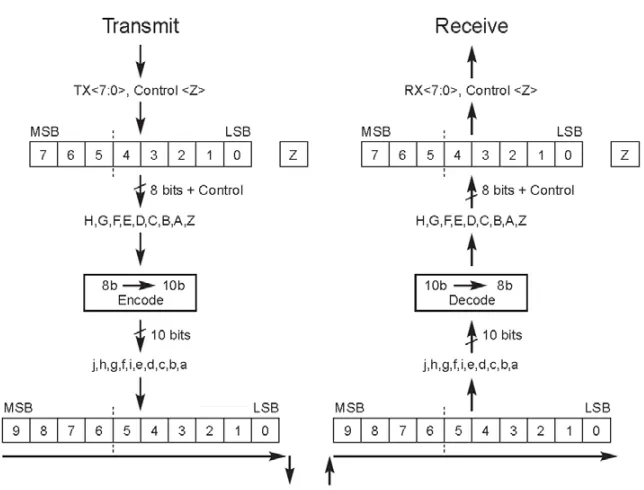

8/10b编码

8/10b编码的作用是为了维持DC平衡,也就是电信号的0和1均匀分布(避免出现5个连续的1或0),8/10b的编码模型只在低于8GT/s下使用,故有必要介绍一下。8/10b的意义在于将8bit的信息按照3bit+5bit分割,填充成4bit+6bit作为10b使用。填充图解如下

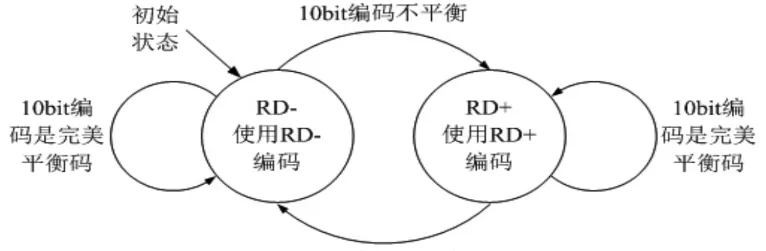

这里填充还分为rd+和rd-模式。RD(running disparity),+/-是1的个数减去0的个数.默认选择rd-

其逻辑为,先默认按照rd-编码,如果是完美平衡码,则不变,如果不是,则转换极性作为rd+编码。 例如:D.x.3(011),其对应的4B码字有两种:1100和0011,此时RD为负,则取1100作为其对应的4B码字作为输出,发现是完美编码

再例如D.x.4(100),其对应的4B码字有两种:1101和0010,若此时RD为负,则取1101作为其对应的4B码字作为输出,但不是完美编码,1101的1的个数大于0的个数,则转换成相反极性,故转换极性为rd+,则默认编码为0010

如下图

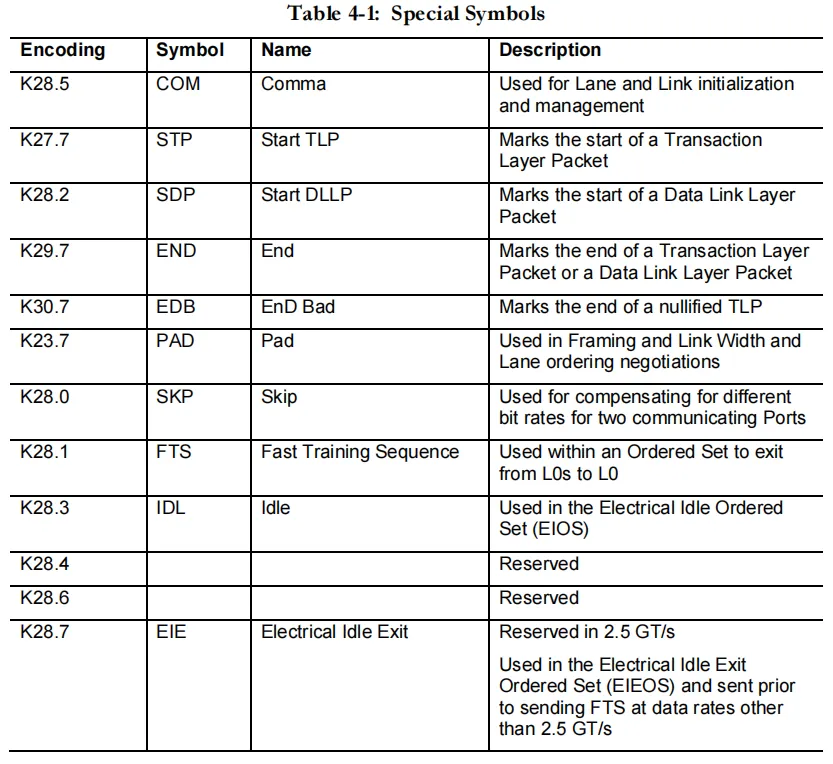

对于特殊的符号编码,如下可知

上述举例

- STP:在开始TLP包前,使用K27.7的符号作为STP符号

- SDP:在开始DLLP包前,使用K28.2的符号作为SDP符号

具体图解如下:

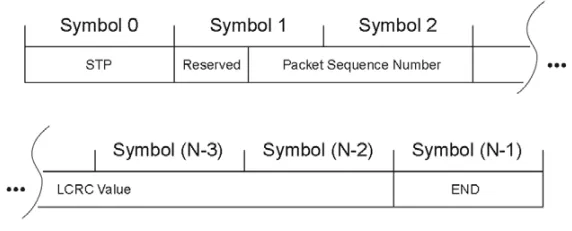

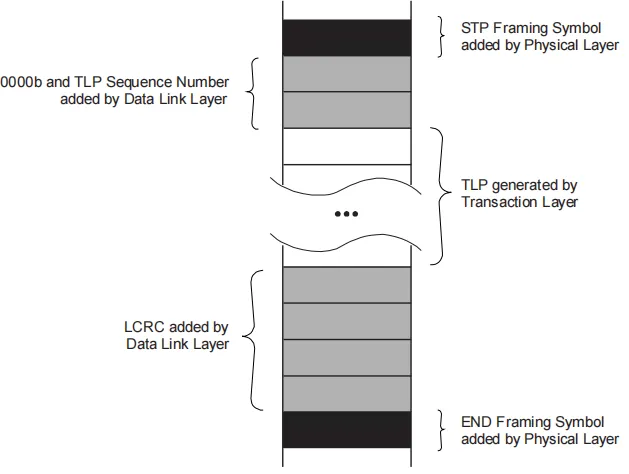

对于TLP,包组成如下,这里物理层会在DLLP的TLP包上追加前缀符号STP和后缀符号END

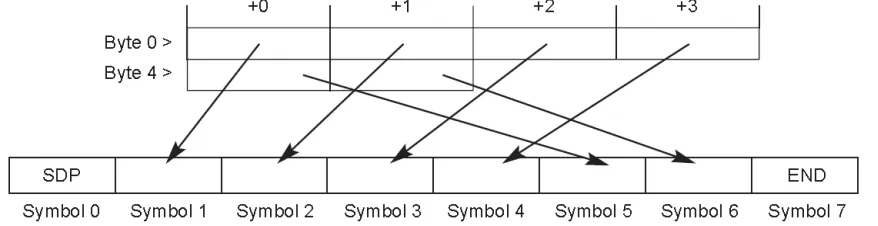

对于DLLP,包组成如下,这里物理层会在DLLP的包上追加前缀符号SDP和后缀符号END

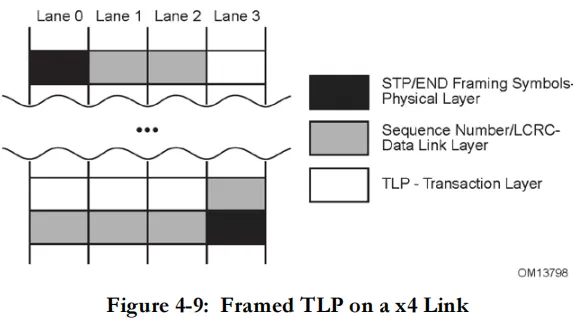

多lane数据的8/10b编码

如果是x1,则物理层按照上述编码即可,如下图

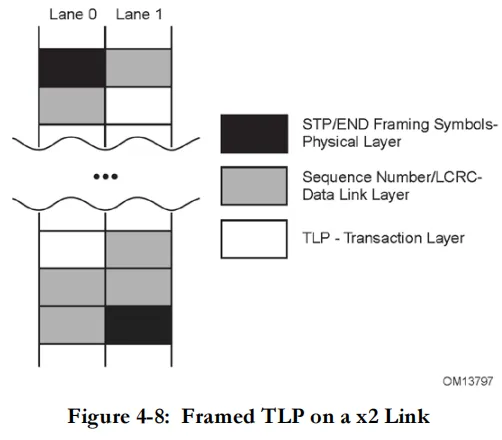

如果是x2,则数据是均匀分布,以TLP包为例,STP在lane0的开头,END在lane1的结束,如图

如果是x4,则如图

数据加扰

在8/10b的编码下,数据发送是先加扰在编码,数据接收是先解码在解扰。加扰解扰是通过LSFR(Linear Feedback Shift Registers)

LSFR计算方式不想明白,这里不介绍了。

128/130b编码

128/130b编码是在8GT/s速度以上,也就是pcie最后速度协商在pcie gen3以上启用。

128/130b的编码是在原128b上添加2b的头,H0和H1,类型如下:

- 10b :代表是一个数据块

- 01b :代表是一个Ordered Set块(有序设置块)

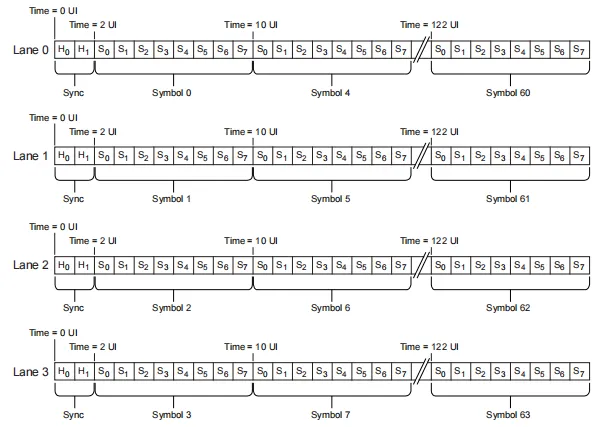

与8/10b不一样的是,在多lane的情况下,128/130b会在每个lane上传输H0/H1头,对于每个数据内容,按照小端方式存放

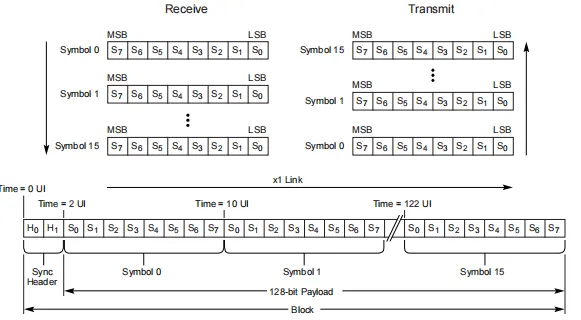

如下是1lane的传输方式

如下是4lane的传输方式

Ordered Set Blocks

在link training的阶段,可以通过特殊的有序集来判断块对齐,这个特殊的有序集就是电气空闲退出有序集(EIEOS),下面是通过EIEOS来判断对齐状态的逻辑

- 未对齐阶段: 接收器在电气空闲后进入未对齐状态,例如刚进入128/130b编码或者退出低功耗状态,如果等待到下一个EIEOS,则进入对齐阶段

- 对齐阶段: 接收器接收EIEOS和SDS(Start of Data Stream)有序集时进入对齐阶段,如果接收到SDS有序集,接收器进入锁定阶段,如果接收到00b或11b的header,则返回未对齐阶段

- 锁定阶段: 这个阶段下,数据块将在SDS Ordered Set后正常发送。

Data Block

数据块由Framing Tokens 和 TLPS 和DLLPS组成,它以SDS Ordered Set开始,以SKP Ordered Set结束。

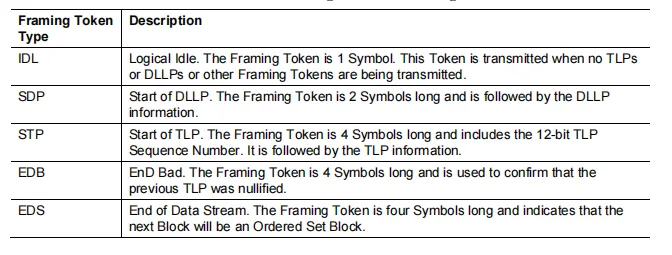

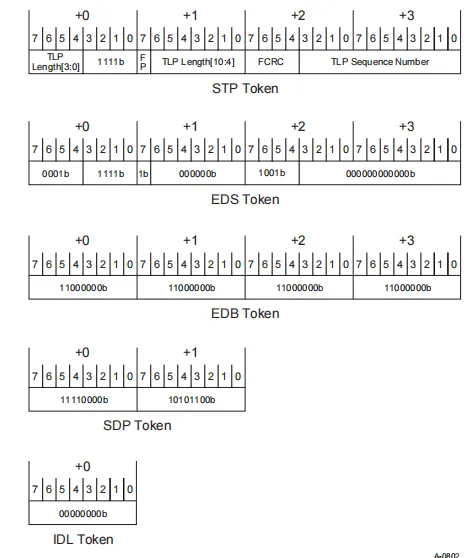

对于Framing Tokens主要有如下几类

- IDL:没有TLPs和DLLPs或其他Framing Tokens传输时,传输此

- SDP:开始DLLP包的Tokens,后面跟随DLLP包

- STP:开始传输TLP包的Tokens,后面跟随12bit的TLP序列号,在后面是TLP包

- EDB:End错误,用于确认之前的TLP包被取消

- EDS:数据流结束,表示数据流结束,下一个块将是Ordered Set Block

上述几类令牌的具体格式如下所示

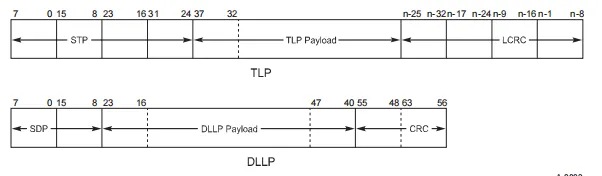

所以对于TLP和DLLP的整体包格式图如下

如上图,TLP包含STP+TLP Prefix(如有)+TLP Header+TLP Payload+TLP 摘要(如有)+LCRC。 如果一个TLP有3DW的Header,1DW的payload,不包括TLP摘要,则整体TLP的length的长度为6=1(Tokens)+0(TLP Prefix)+3(TLP Header)+1(Payload)+0(TLP digest)+1(LCRC)

对于DLLP则简单了,就是在DLLP上加上SDP的Token,即SDP+DLLP+CRC

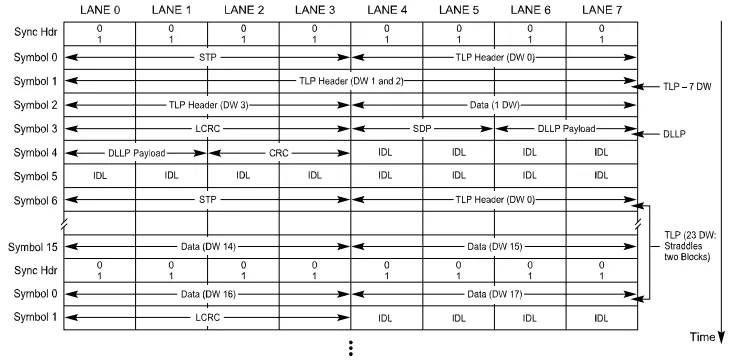

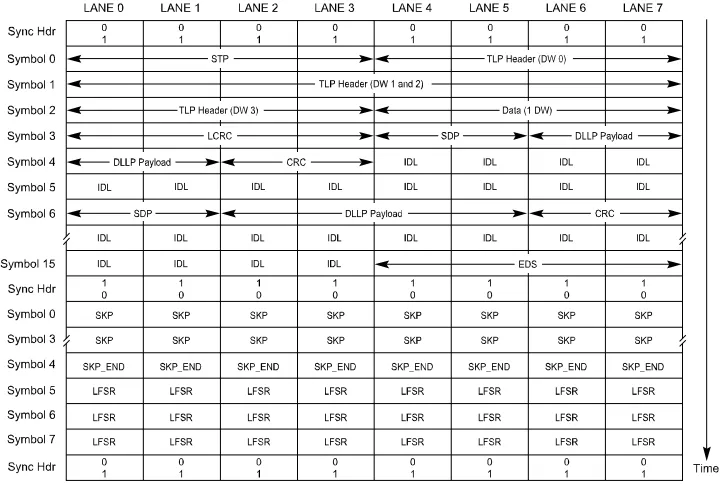

对于x8的lane的pcie接口,总包数据传输如下所示

从上面可以知道,对每个lane,H0/H1都是存在的,而Tokens+TLP+DLLP则是均匀遍布在每个lane上。具体为:STP+TLP Header+TLP Payload+LCRC+SDP+DLLP+CRC+IDL+STP....

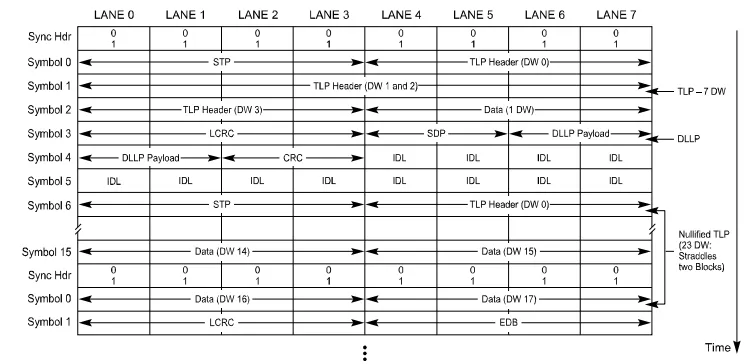

对于取消TLP是整包示例如下

这里值得注意的是,EDB的Tokens是作为TLP的扩展,它不计算在TLP的lenth字段中,所以TLP包在传输的过程中,会直接带一个EDB作为TLP的取消。

之前提到了SKP作为整个数据库的结束,故如下图展示带SKP Tokens的整包示例

可以看到,在EBS之后,新的包是10+SKP+SKP_END+LSFR。故SKP Ordered Set作为整个数据块的结束

数据加扰

通过LSFR加扰,在128b/130b下,前两位H0/H1不会被加扰,EIEOS Ordered Set,SDS,SKP, EIOS不会加扰,LSFR会在EIEOS发送后加扰(有效数据加扰),在EIEOS接收后解扰(接收器解扰数据)。