目录

PCIE物理层-链路初始化与训练

link trainning 通过LTSSM(Link Training and Status State Machine)完成。在这个过程中,可以发现并确定如下:

- 链路带宽

- 链路速率

- 链路反相

- 链路极性

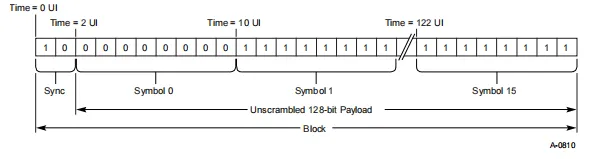

Training Sequences

训练时序由位对齐,符号对齐和交换物理层参数三个部分组成,

TS1和TS2用来传输PCIE链路的配置信息

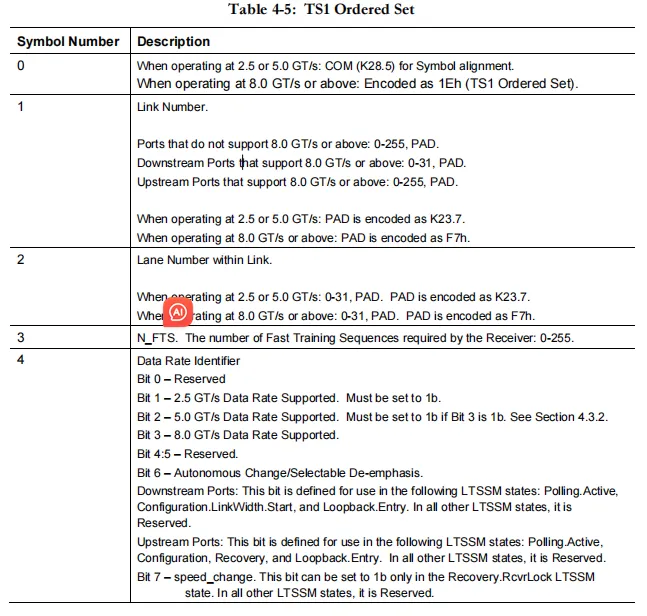

TS1 Ordered Set的具体符号描述如下

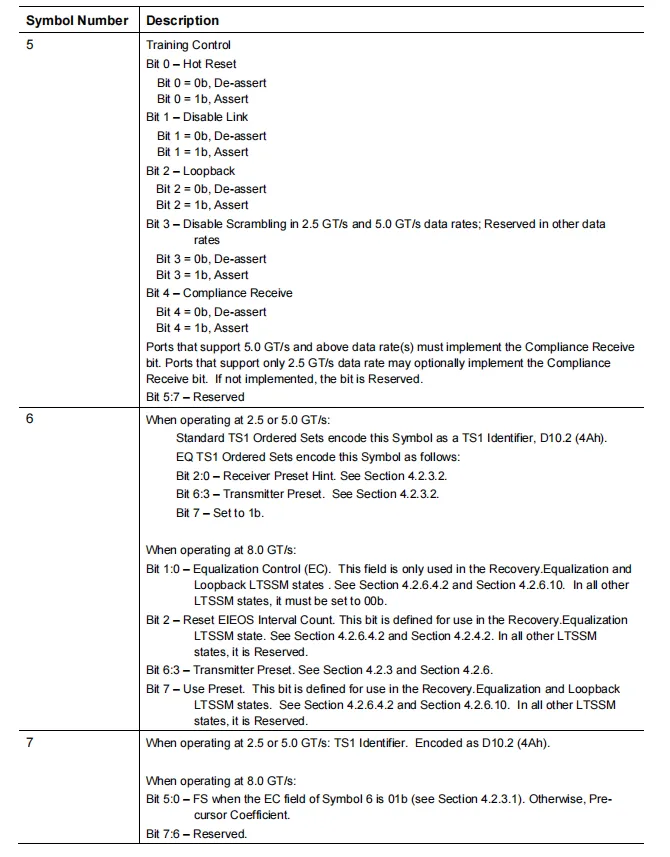

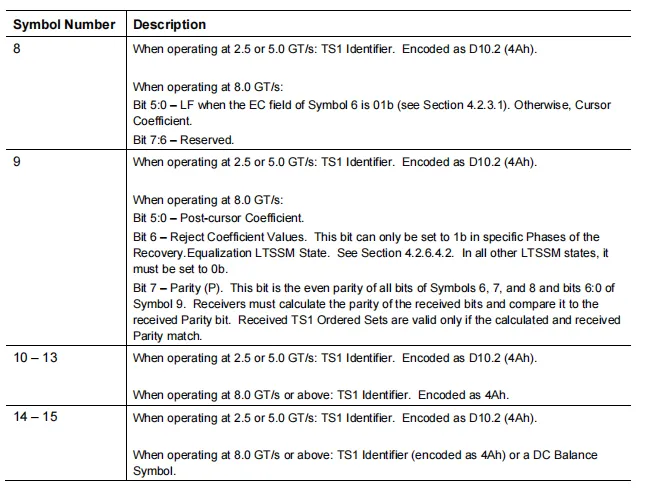

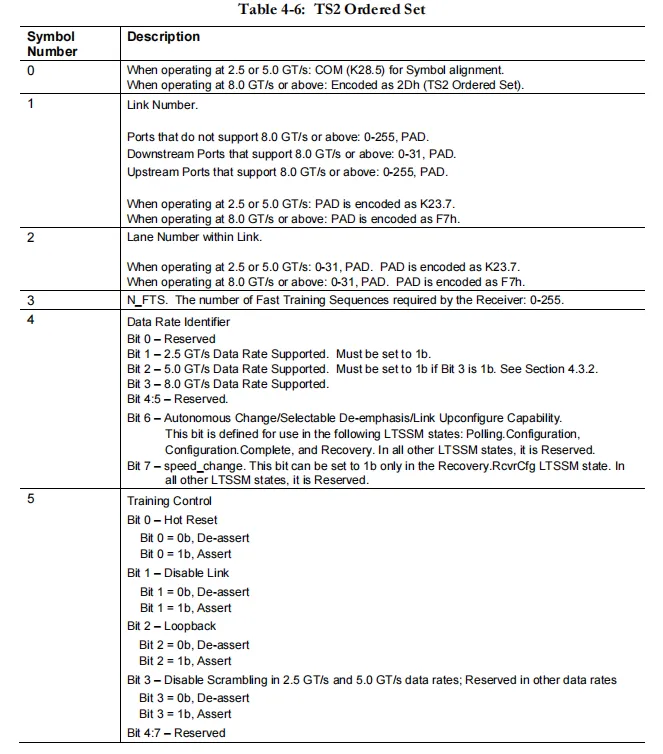

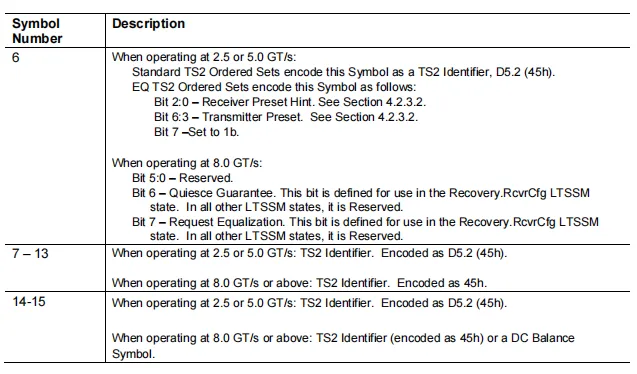

TS2 Ordered Set的具体符号描述如下

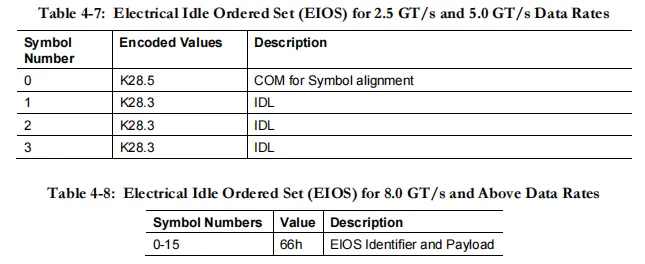

EIOS

在发送器进入电气空闲状态时,必须发送EIOS Ordered Set

- 在使用8/10b的时候,EIOS是K28.5(COM)+ 3个K28.3(IDL)符号组成

- 在使用128/130b的时候,EIOS是16个符号的数据,接收器再接收第4个符号的时候,就已经代表接收到了一个EIOS。

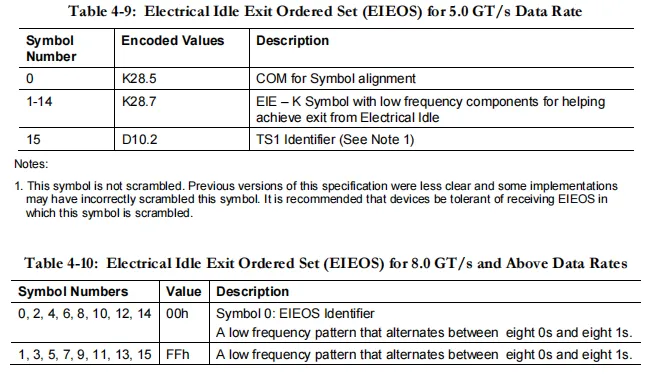

EIEOS

EIEOS用作确保能够检测到电气空闲退出状态,当使用128/130b时,还用于块对齐

EIEOS在5.0GT/s的符号格式(8/10b)和8.0GT/s的符号格式(128/130b)如下

gen3的EIEOS数据块格式如下

链路极性

在training的过程中,TS1和TS2的符号6-15作为链路极性标志,如果极性反转,则

- TS1的6-15符号是D21.5而不是D10.2

- TS2的6-15符号是D26.5而不是D5.2

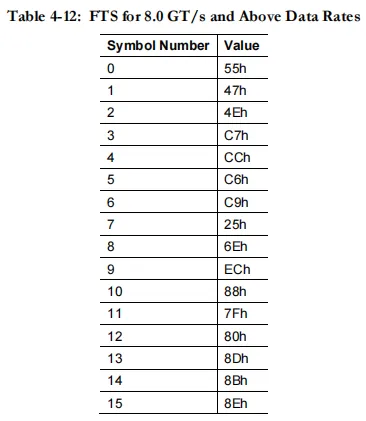

FTS(Fast Training Sequence)

在L0s到L0过渡时用于位锁定和符号锁定,FTS的符号信息如下

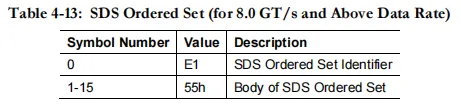

SDS

作为数据块的开始符号,在 Configuration.Idle, Recovery.Idle, 和 Tx_L0s状态下传输,SDS的符号信息如下

链接错误恢复

链路错误主要发生在解码错误,帧错误,符号丢失,缓冲区溢出或丢失,块对齐,错误通常发生在L0状态,也会在L0到Recovery上发生。如不在L0状态上发生的链接错误,LTSSM状态机不会转换到Recovery上。

链路速率协商

协商的行为主要是先从2.5GT/s上启动Link Training,然后在Training Sequence(TS1/TS2)中可以获取支持的速率大小,然后以2.5GT/s的速率走到L0状态,然后从L0走到Recovery状态,重新开始以新的速率Link Training。

链路Width和Lane顺序协商

对于pcie的带宽根据pcie的协议版本来决定,同样的pcie的总体带宽根据lane的数量来决定。

对于pcie来说,gen3可以兼容gen1,对于lane来说,可以将x8拆分成x4+x4。

对于pcie的lane顺序来说,lane可以交织,也就是lane0可以接lane3,lane1接lane2,lane2接lane1,lane3接lane0

也就是说,对于pcie3.0 x16来说。可以作为单纯的x16的gen3连接,也可以作为2个x8.或4个x4,或16个x1,同时对于每个lane,都可以是gen3(8GT)或gen2(5GT)或gen1(2.5GT)

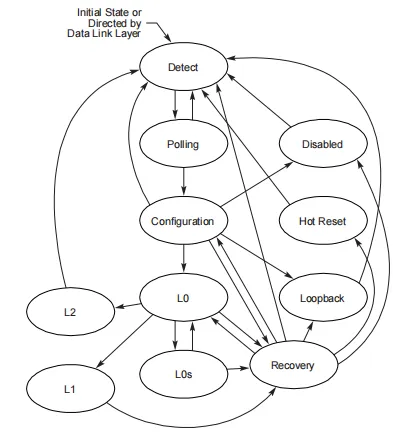

LTSSM状态机

LTSSM状态机如下所示

每个阶段的解释如下

- Detect: 检测pcie是否存在,存在则进入此状态

- Polling: 端口已经发送Training Ordered Sets并接收到Training Ordered Sets,此时已经位锁定和符号锁定,lane极性也确定好了

- Configuration:在基于确定的速率上发送和接收数据, lane的width和lane顺序也确定好了

- Recovery: 恢复阶段开始配置新的速率,然后重新位锁定,符号锁定和块对齐,以及通道去偏移

- L0:正常运行状态,数据和控制包正常发送和接收

- L0s:L0的低功耗状态,在接收到EIOS后进入L0s状态,但是L0s恢复到L0时需要重新位锁定,符号锁定和块对齐,以及通道去偏移

- L1:节能状态,但是L1的resume将比L0s时间更长,通过数据链路层的指令并接收到EIOS之后来进入L1状态

- L2:更节能的状态,此时接收器和发送器已经关闭,主电源和时钟信号都可能停止,但是辅助电源还是可用,也是通过数据链路层的指令并接收到EIOS之后来进入L2状态

- Disabled:通过配置链路的方式禁用电气空闲退出状态,Disabled使用 1位(Disable link 位)来发送(在TS1/TS2中),禁用通过更高的协议层设置进入禁用状态,也可以发送连续两个带禁用bit的TS1 Oedered Set来禁用

- Loopback: 用于测试和故障隔离,回环标志在TS1/TS2的bit 2,连续两个设置回环的TS1可以进入回环。

- Hot Reset:热重置在TS1/TS2的Training Control域,连续两个设置热重置的TS1可以进入热重置

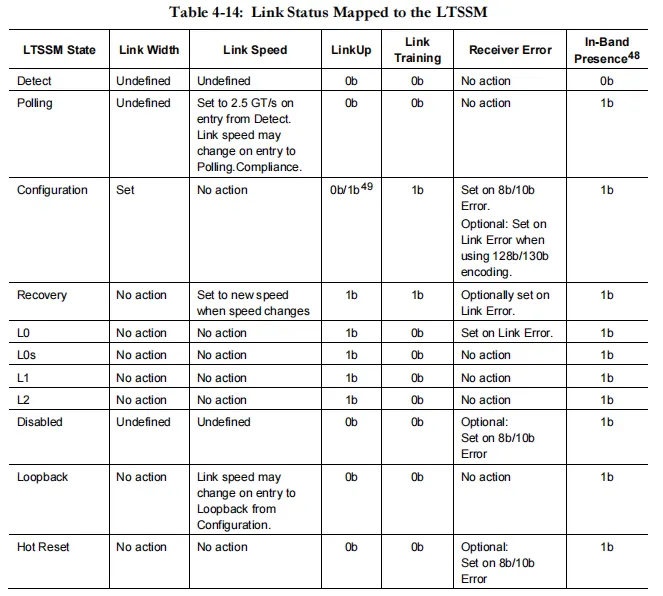

对于LTSSM状态机的状态情况下的Link Status如下图

从上图可以知道,例如LinkUp状态,在Configuration时可能是1可能是0,这是指的如果是从detect--->polling--->configuration,则此时是0,到recivery才是1.但是如果是从recovery或其他状态进入configuration,则此时的link up是1

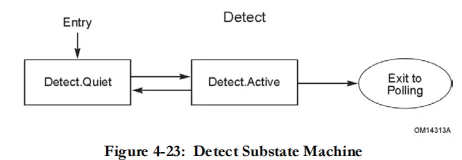

Detect子状态机

Detect的默认状态从Quiet开始,然后默认以2.5GT/s进行均衡,均衡完成之后,等待12ms超时或电气空闲状态Broken后,进入Active,在进入active后的再一个12ms内检测接收器,如果在lane上接收到Detection Sequence,则进入Polling,否则进入quiet。

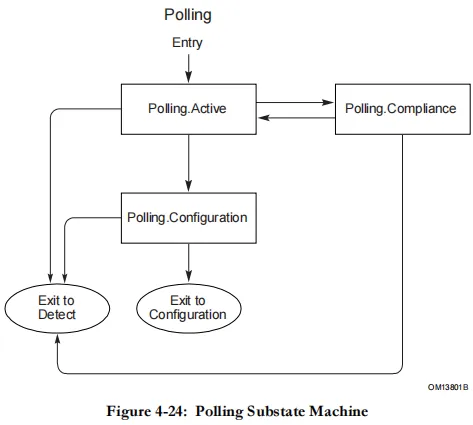

Polling子状态机

发送器先进入Active状态

- 如果从Link Control 2寄存器的bit4获取值为1,则进入Compliance状态

- 如果已连续发送1024个TS1,这个TS1的通道和链路编号设置为PAD后进入Configuration

- 否则在24ms超时后判断,Compliance标志如果清空,则进入Configuration,如果是1,则进入Compliance,如果都没有设置,则退出到Detect阶段

如果在Configuration状态

- 如果接收到发送的8个TS2并且设置了PAD,并且在接收到1个TS2时发送16个TS2,则进入Configuration

- 否则在48ms超时后退回到Detect

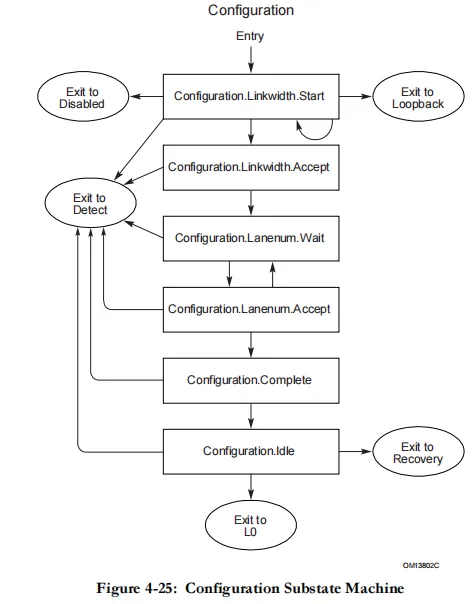

Configuration子状态机

- 对于configuration状态机,最开始进入start

- 如果检测到TS1/TS2的禁用标志,则进入Disabled

- 如果收到两个连续的TS1,其链路号与PAD不同且通道号设置为PAD,则进入Accept

- 24ms超时后进入Detect

其他细节不详述,(见4.2.6.3)如下图所示

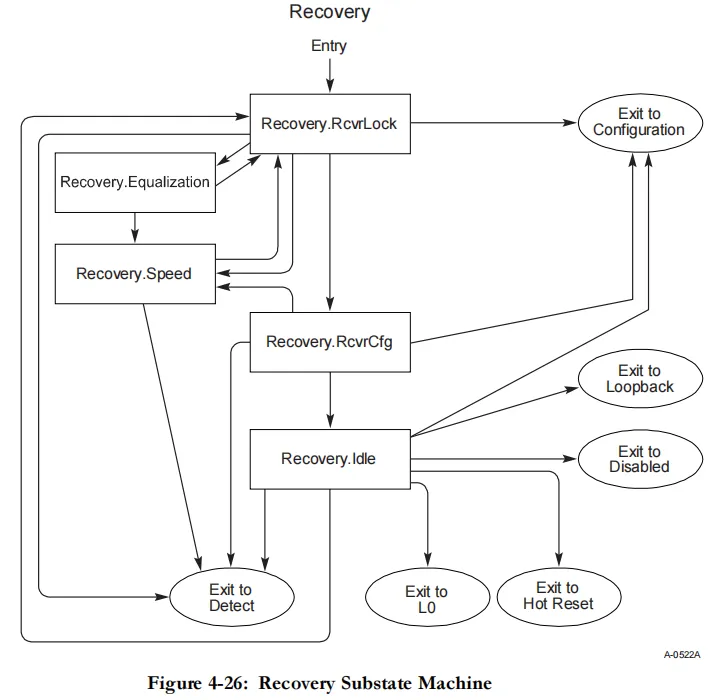

Recovery子状态机

Recovery的子状态机如下所示,不详述

L0

L0没有子状态机,如果处于L0,在改变Link Width时进入Recovery,也可以进入L0s,或L1或L2状态。

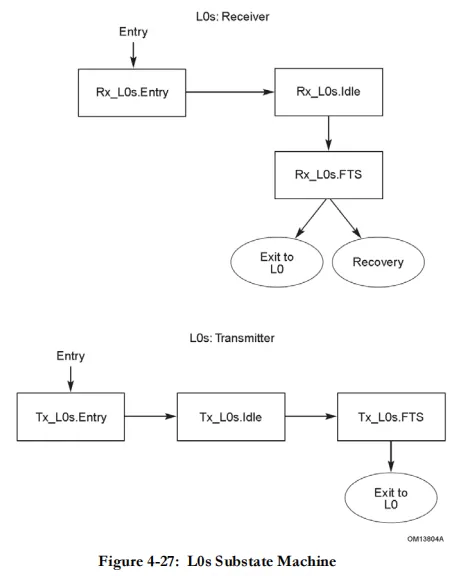

L0s子状态机

通过FTS可以进入L0状态

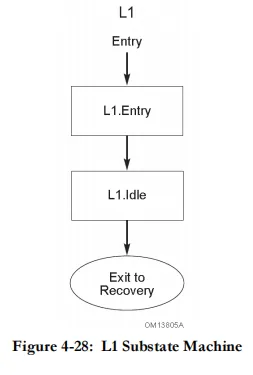

L1子状态机

当长时间没有TLP和DLLP时,发送端通知接收端进入L1状态,如果接收端不同意则进入L0s状态,如果同意则进入L1状态

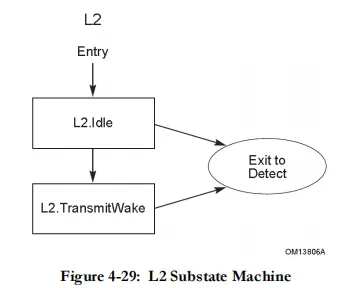

L2子状态机

L2状态属于更节能的状态,所以都会重新Detect,与L0,L0s,L1不同的是,它们都是通过Recovery

Disabled

Disabled没有子状态机,当禁用标志位起来时就是Disabled状态机,如果标志清空,则重新进入Detect

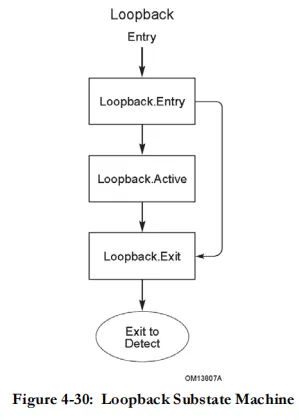

Loopback子状态机

回环通过配置进入,如果退出回环则重新detect,状态机如下

Hot Reset

Hot Reset没有子状态机,默认通过控制进入Hot Reset,或者接收两个连续的TS1,并带有Hot Reset标志作为进入Hot Reset