目录

之前把rtems上支持的所有的调度器介绍了一遍,但是一直都没有说上下文是如何切换的。其实上下文切换的逻辑就是保存线程TCB和通用寄存器,然后根据新的线程TCB信息进行运行。本文从上下文切换的角度来讲清楚RTEMS中是怎么完成上下文切换的

从schedule函数角度看

对于任何的任务,调用schedule就是根据当前任务的情况执行调度,那么主动调用如下函数

( *scheduler->Operations.schedule )( scheduler, the_thread );

这里不同的调度算法实现的回调不一样,为了方便介绍,这里以优先级调度为例,那么最后调用函数如下

static inline void _Scheduler_uniprocessor_Update_heir( Thread_Control *heir, Thread_Control *new_heir ) { _Assert( heir != new_heir ); #if defined(RTEMS_SMP) /* * We need this state only for _Thread_Get_CPU_time_used_locked(). Cannot * use _Scheduler_Thread_change_state() since THREAD_SCHEDULER_BLOCKED to * THREAD_SCHEDULER_BLOCKED state changes are illegal for the real SMP * schedulers. */ heir->Scheduler.state = THREAD_SCHEDULER_BLOCKED; new_heir->Scheduler.state = THREAD_SCHEDULER_SCHEDULED; #endif _Thread_Update_CPU_time_used( heir, _Thread_Get_CPU( heir ) ); _Thread_Heir = new_heir; _Thread_Dispatch_necessary = true; }

再设置完一些state之后,我们重点关注如下两个值的设置

_Thread_Heir = new_heir; _Thread_Dispatch_necessary = true;

这里的new_heir是即将要运行的任务,他是Thread_Control * 指针。而_Thread_Dispatch_necessary是Per_CPU_Control结构体的一个成员dispatch_necessary,我们通过dispatch_necessary来判断当前任务是否要scheduler。

从_Thread_Do_dispatch函数角度看

我们当任务在合适的实际,我们可以设置dispatch enable,或者直接调用_Thread_Do_dispatch函数,这样线程就直接开始开始调度的实际行为。 我们看起核心代码如下

do { Thread_Control *heir; heir = _Thread_Get_heir_and_make_it_executing( cpu_self ); if ( heir == executing ) { break; } _ISR_Local_enable( level ); _Thread_Save_fp( executing ); _Context_Switch( &executing->Registers, &heir->Registers ); _Thread_Restore_fp( executing ); _User_extensions_Thread_switch( NULL, executing ); cpu_self = _Per_CPU_Get(); _ISR_Local_disable( level ); } while ( cpu_self->dispatch_necessary );

可以看到,只要dispatch_necessary设置为true,那么任务就会执行调度。执行调度的函数为_Context_Switch,它会根据每个架构的实现来运行上下文切换,我们基于armv8架构来介绍

从_CPU_Context_switch函数来看

这里主要是Arm64的实现,先看源码

DEFINE_FUNCTION_AARCH64(_CPU_Context_switch) .globl _CPU_Context_switch_no_return .set _CPU_Context_switch_no_return, _CPU_Context_switch #ifdef AARCH64_MULTILIB_ARCH_V8_ILP32 /* Sanitize inputs for ILP32 ABI */ mov w0, w0 mov w1, w1 #ifdef RTEMS_SMP #define reg_2 x2 #else #define reg_2 w2 #endif #else #define reg_2 x2 #endif /* Start saving context */ GET_SELF_CPU_CONTROL reg_2 ldr w3, [x2, #PER_CPU_ISR_DISPATCH_DISABLE] // 读取isr_dispatch_disable stp x19, x20, [x0] // 保存aapcs中规定的callee寄存器 也就是x19-x28 stp x21, x22, [x0, #0x10] stp x23, x24, [x0, #0x20] stp x25, x26, [x0, #0x30] stp x27, x28, [x0, #0x40] stp fp, lr, [x0, #0x50] // 保存fp和lr mov x4, sp // 保存sp寄存器 str x4, [x0, #0x60] #ifdef AARCH64_MULTILIB_VFP add x5, x0, #AARCH64_CONTEXT_CONTROL_D8_OFFSET stp d8, d9, [x5] // 保存浮点寄存器 stp d10, d11, [x5, #0x10] stp d12, d13, [x5, #0x20] stp d14, d15, [x5, #0x30] #endif str x3, [x0, #AARCH64_CONTEXT_CONTROL_ISR_DISPATCH_DISABLE] //将本线程的isr_dispatch_disable设置到x0 #ifdef RTEMS_SMP /* * The executing thread no longer executes on this processor. Switch * the stack to the temporary interrupt stack of this processor. Mark * the context of the executing thread as not executing. */ dmb SY //所有数据dmb add sp, x2, #(PER_CPU_INTERRUPT_FRAME_AREA + CPU_INTERRUPT_FRAME_SIZE) //分配一个栈 mov x3, #0 //将0写到is_executing中 strb w3, [x0, #AARCH64_CONTEXT_CONTROL_IS_EXECUTING_OFFSET] .L_check_is_executing: /* Check the is executing indicator of the heir context */ add x3, x1, #AARCH64_CONTEXT_CONTROL_IS_EXECUTING_OFFSET //获取is_executing的值 ldaxrb w4, [x3] //原子读取x3的内容到w4 cmp x4, #0 bne .L_get_potential_new_heir //如果已经其他cpu执行则跳到其他线程tcb上重新判断 /* Try to update the is executing indicator of the heir context */ mov x4, #1 stlxrb w5, w4, [x3] // 将is_executing设置回去,结果保存在w5 cmp x5, #0 bne .L_get_potential_new_heir // 如果设置失败,则跳到其他tcb上重新判断 dmb SY // dmb所有数据 #endif /* Start restoring context */ .L_restore: #if !defined(RTEMS_SMP) && defined(AARCH64_MULTILIB_HAS_LOAD_STORE_EXCLUSIVE) clrex // 清空独占监视器 #endif ldr x3, [x1, #AARCH64_CONTEXT_CONTROL_THREAD_ID_OFFSET] // 加载下一个线程的thread_id ldr x4, [x1, #AARCH64_CONTEXT_CONTROL_ISR_DISPATCH_DISABLE] // 加载下一个线程的isr_dispatch_disable #ifdef AARCH64_MULTILIB_VFP add x5, x1, #AARCH64_CONTEXT_CONTROL_D8_OFFSET // 加载下一个线程的浮点寄存器 ldp d8, d9, [x5] ldp d10, d11, [x5, #0x10] ldp d12, d13, [x5, #0x20] ldp d14, d15, [x5, #0x30] #endif msr TPIDR_EL0, x3 // 将x3设置到TPIDR_EL0 str w4, [x2, #PER_CPU_ISR_DISPATCH_DISABLE] // 更新isr_dispatch_disable ldp x19, x20, [x1] // 恢复下一个线程的callee寄存器 ldp x21, x22, [x1, #0x10] ldp x23, x24, [x1, #0x20] ldp x25, x26, [x1, #0x30] ldp x27, x28, [x1, #0x40] ldp fp, lr, [x1, #0x50] // 恢复fp和lr ldr x4, [x1, #0x60] mov sp, x4 //恢复sp ret

上面代码尽可能给出了注释,有些补充解释如下

x0和x1

我们知道_CPU_Context_switch的原型是:

_CPU_Context_switch( _executing, _heir )

所以x0 是当前线程tcb,x1是下一个线程的tcb

Context_Control结构体

我们知道需要保存x19-x30 sp等寄存器,那么保存的地方在TPIDR_EL0上,TPIDR_EL0上存在的是Context_Control的指针,所以Context_Control结构体如下。

typedef struct { uint64_t register_x19; uint64_t register_x20; uint64_t register_x21; uint64_t register_x22; uint64_t register_x23; uint64_t register_x24; uint64_t register_x25; uint64_t register_x26; uint64_t register_x27; uint64_t register_x28; uint64_t register_fp; uint64_t register_lr; uint64_t register_sp; uint64_t isr_dispatch_disable; uint64_t thread_id; #ifdef AARCH64_MULTILIB_VFP uint64_t register_d8; uint64_t register_d9; uint64_t register_d10; uint64_t register_d11; uint64_t register_d12; uint64_t register_d13; uint64_t register_d14; uint64_t register_d15; #endif #ifdef RTEMS_SMP volatile bool is_executing; #endif } Context_Control;

dmb SY

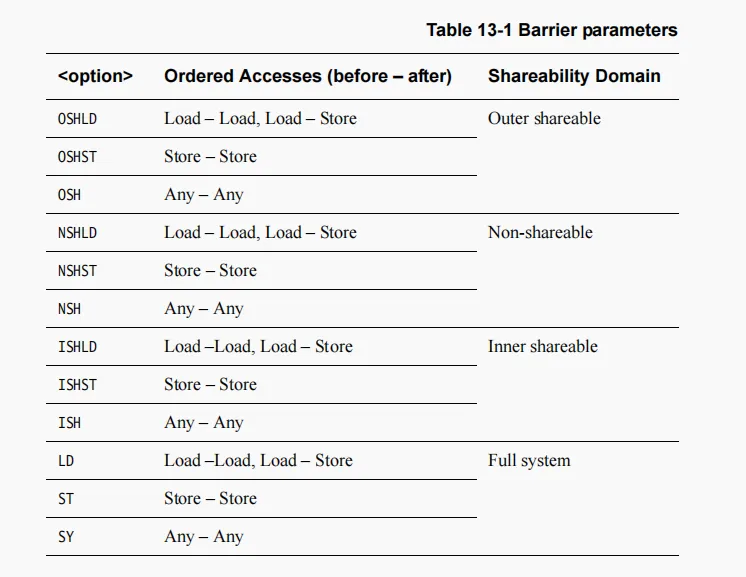

dmb是数据内存同步,SY是对全系统进行刷新,SY的解释如下

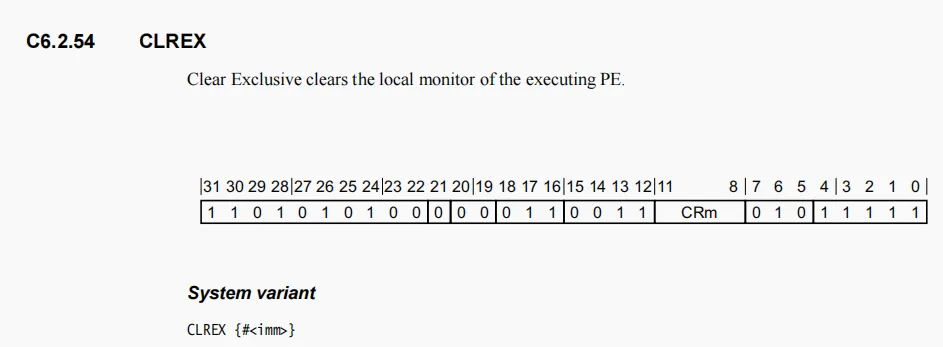

CLREX

Clear Exclusive access monitor,清空独占监视器,请问接下来要做独占访问,这里直接清空独占监视器

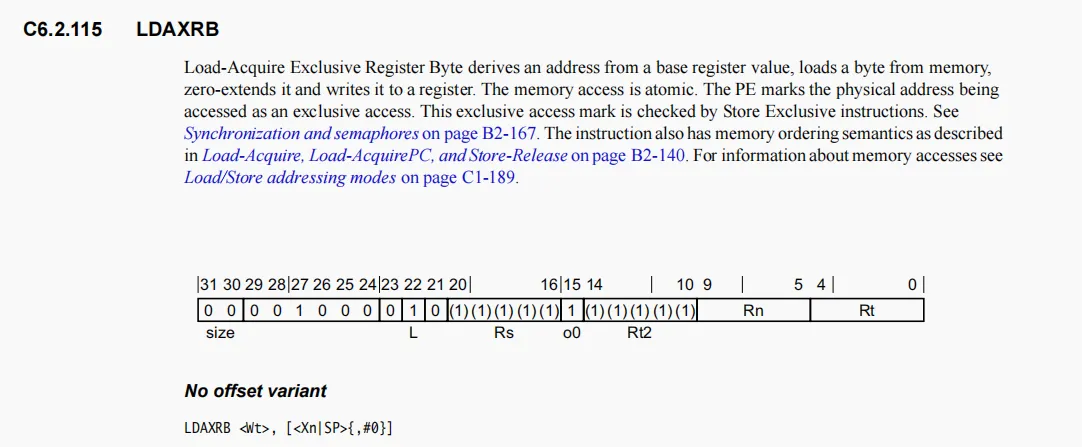

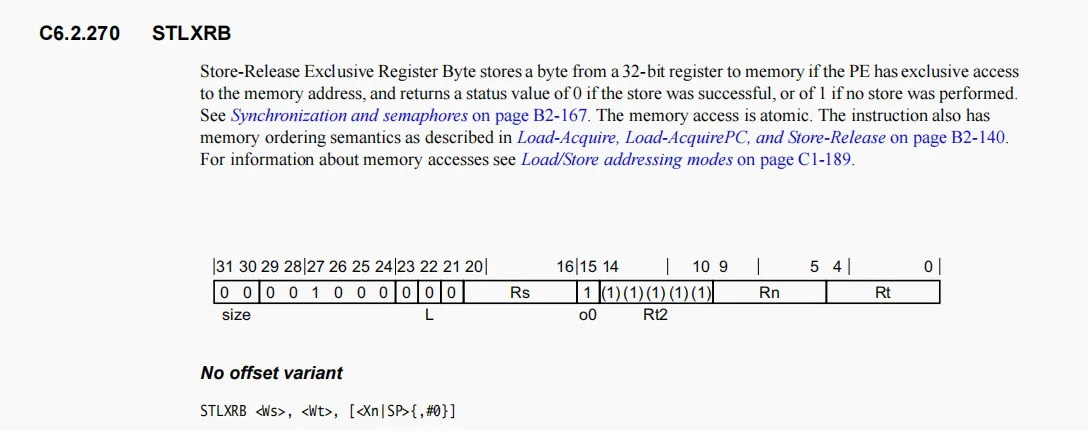

ldaxrb和stlxrb

这两个都是独占访问内存和独占存储内存,

其中stlxrb会将"<Ws>"的值返回出来,如果是0则独占访问成功,如果非0则失败

总结

至此,我们根据上下文切换的代码分析,清楚的知道了调度器在任务运行时的寄存器保存过程和sp分配过程等。相关演示操作在之前的文章有过体现,gdb能够很清楚的看到任务分配后的寄存器显示,这里就没有必要重复了。