目录

aarch64中,有一个专门配置内存属性表的寄存器,为MAIR,本文基于MAIR寄存器讲解其作用

一、内存属性寄存器

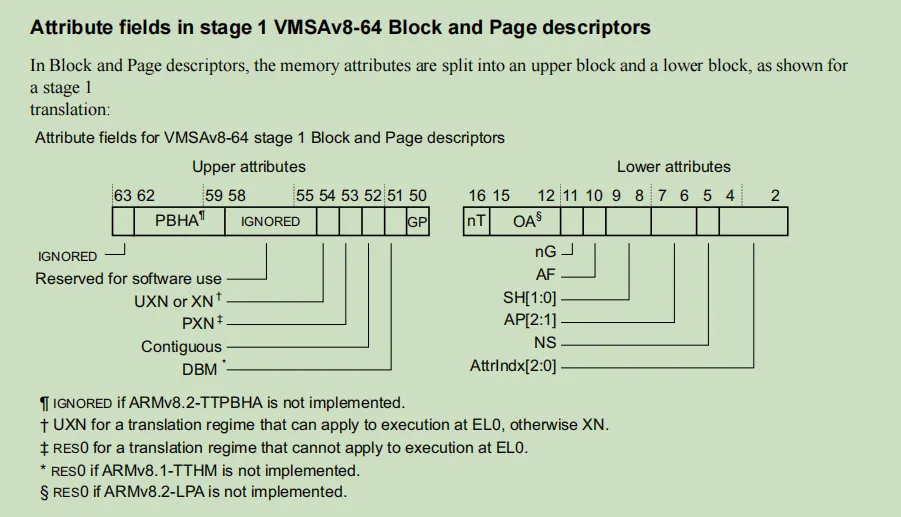

对于虚拟内存地址,我们知道其分布如下

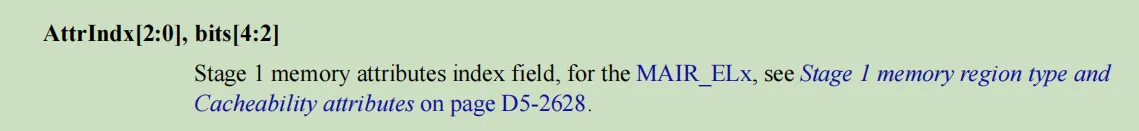

这里我们只关注AttrIndx[2:0],可以知道描述如下:

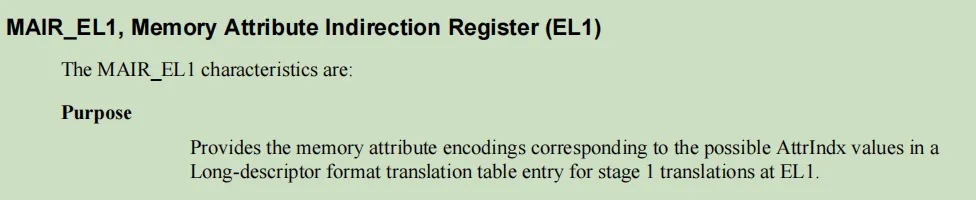

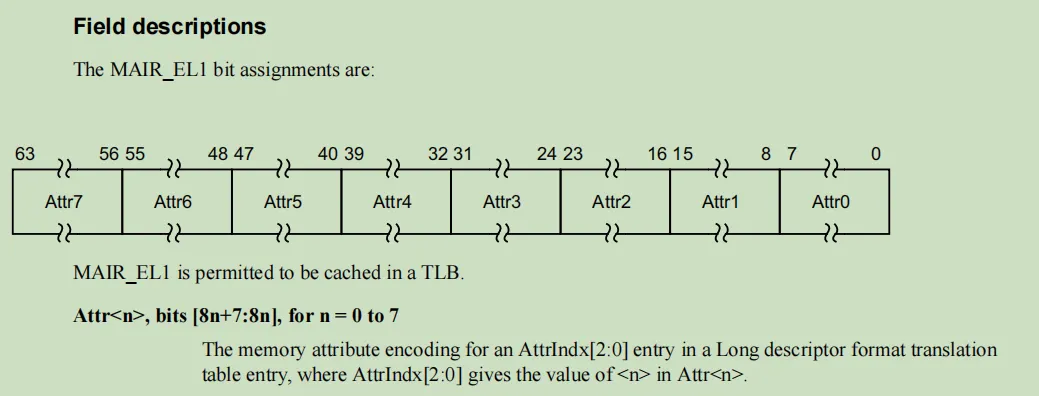

这里stage 1就说ttbrx到pte的过程,这里的bits [4:2]指示的是MAIR寄存器中attr的索引。而MAIR寄存器如下 以el1为例

这里mair有8个attr,如下

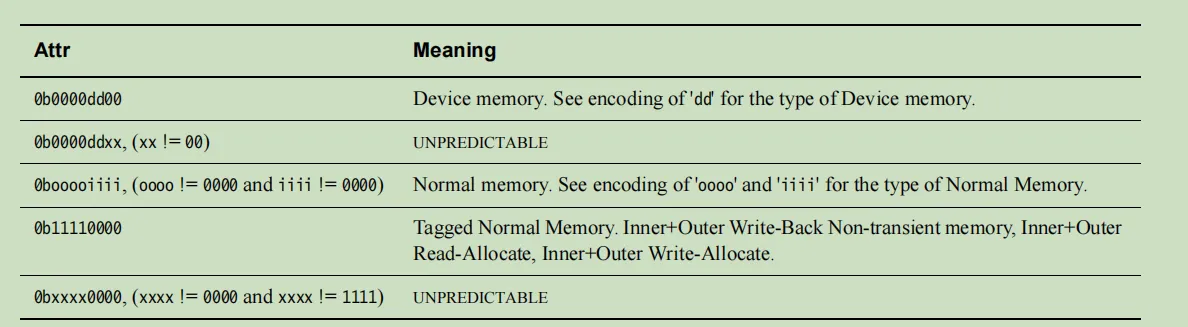

这里的attr的值含义如下

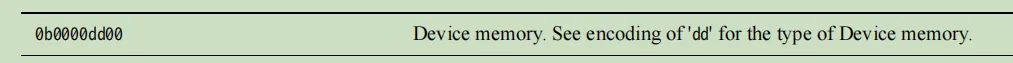

其中熟悉可以分为设备内存和正常内存,如下

- Device Memory

- Normal Memory

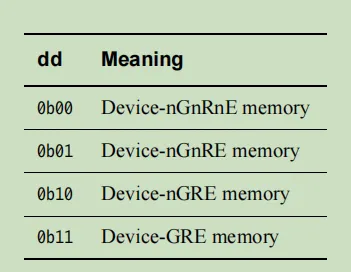

通过dd位区分,如下

这里我们看到GRE三个概念,解释如下

- G: Gathering 是否可合并。 表示对多个memory的访问是否可以合并,如果是nG,表示处理器必须严格按照代码中内存访问来进行,不能把两次访问合并成一次

- R: Reordering 是否可指令重排 表示是否允许处理器对内存访问指令进行重排。nR表示必须严格执行program order。

- E: Early Write Acknowledgement 是否提前写应答 表示对于write而言的ack时机,为了加快写的速度,系统的中间环节可能会设定一些write buffer。nE表示写操作的ack必须来自最终的目的地而不是中间的write bufferr。

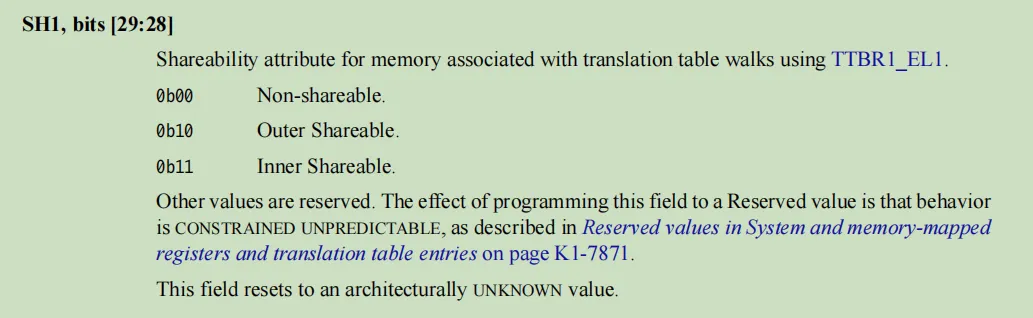

关于memory的shareable补充如下:

在TCR_EL1寄存器中,关注sh1 bit[29:28]如下:

这里可以看到

对于aarch64,cpu按照cluster划分,根据cluster的share规则如下

- Non-shareable : cpu之间完全不共享

- Inner-shareable : cpu之间,如果在一个cluster内,共享

- outer-shareable : cpu之间,可以在不同cluster上共享

这里的inner指的是一个cluster内,outer指的非一个cluster内

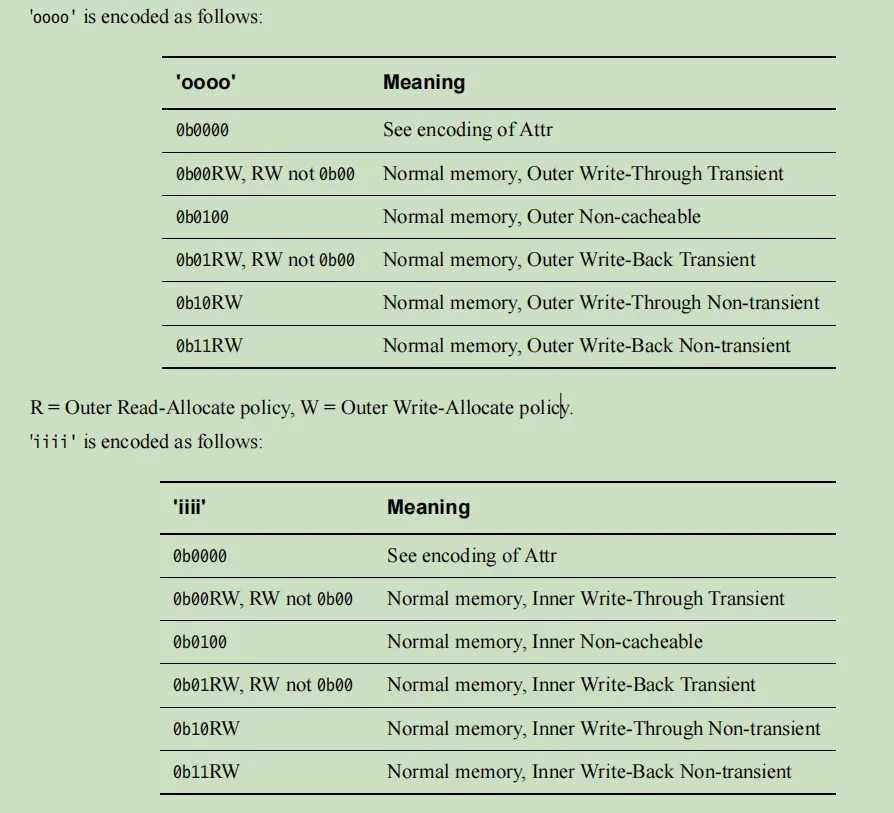

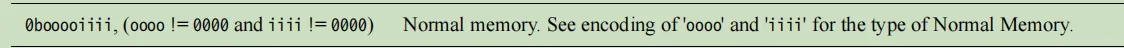

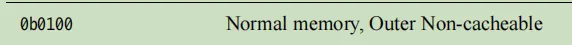

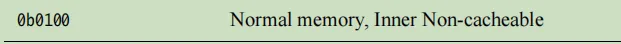

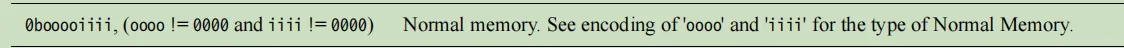

而对于Normal Memory,通过0booooiiii来区分,如下解释

这里oooo是高位,iiii是低位。可以看到,这里对于Normal memory而言,我们看到了cacheable的如下属性

- write-through transient: 短暂写通

- write-back transient : 短暂写回

- write-through: 写通

- write-back:写回

这里写通指的是内存写操作,直接更新到缓存和内存中,也就是缓存和内存数据是一致的

这里写回指的是内存写操作,只更新到缓存中,推迟对内存的更新,直到该缓存行被替换时才写回内存,这种情况下我们可以跟踪dirty bit,如果脏位是1,则缓存和内存的数据不一致

处理cacheable的write方式,还有transient 标志位

- transient 指的是短暂标志

如果带有transient ,则表示内存使用时间很短,可以利用此标志来优先更新cache line

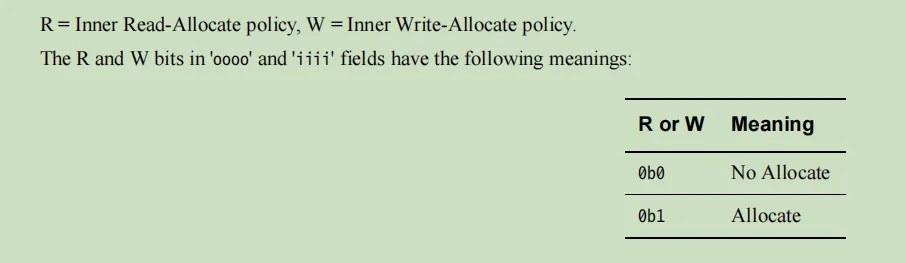

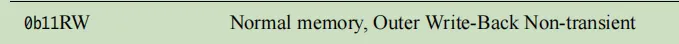

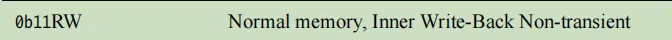

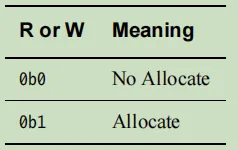

除了这些,我们还可以注意到RW标志,如下解释

这里的RW分别是 Read-allocate和Write-allocate,解释如下:

- Read-Allocate: CPU Read data from Main Memory and Allocate it in cache

read的时候,如果出现miss,则从内存中读取数据,然后申请一个cache line,并记录

- Write-Allocate: CPU Write data to Main Memory and Allocate it in Cache.

write的时候,如果出现miss,先写到内存中,然后申请一个cache line,并记录

如果都是0,则代表No allocate,解释如下

- No Read-Allocate: 读miss时,直接读内存中,不加载到cache

- No Write-Allocate: 写miss时,直接写到内存中,不加载到cache

二、示例计算

假设我设置的MAIR_EL1的值是0xffffffffff440400,这里计算如下

- attr0:0x0

- attr1:0x4

- attr2:0x44

- attr3:0xff

2.1 计算attr0

可以知道,dd也是00,便知道这里是如下:

- Device-nGnRnE memory

也就是 设备内存,不执行合并,不执行指令重排,不执行提前写应答

2.2 计算attr1

可以知道,dd是01,便知道如下:

- Device-nGnRE memory

也就是 设备内存,不执行合并,不执行指令重排,可以提前写应答

2.3 计算attr2

0x44,对应如下

对于oooo如下:

对于iiii如下:

也就是 正常内存,cluster内和cluster之间 都是non-cacheable的,所以的读写操作都是没有cache的。

2.4 计算attr3

0xff,对于如下

对于oooo如下:

对于iiii如下:

这里rw也是11,如下解释

这里是 正常内存,非短暂内存,读 allocate, 写 allocate。 简单来说就是所有的内存带cache,读写操作都经过cache